毛刺 專用HD諧波減速機FHA-8C-50-E200A-C"毛刺",在里也稱作"噪聲"。是行情圖表上出現的與原來大趨勢方向相反的小的回調走勢,往往不易分辨是否轉勢(經常是騙線)。

毛刺 專用HD諧波減速機FHA-8C-50-E200A-C毛刺含義

、銑切、電鍍術語。

毛刺 專用HD諧波減速機FHA-8C-50-E200A-C毛刺 veining

金屬件表面出現余屑和表面極細小的顯微金屬顆粒,這些被稱為毛刺。毛刺越多,其質量標準越低。

鋼材表面缺陷之一,表現為冷切、熱鋸或火焰切割的鋼材端部有不齊的飛邊,焊管時焊縫處有擠出的多余金屬。冷切產品端部毛刺的厚度取決于刀刃間的縫隙。一般產品允許有一定高度的毛刺存在;但焊管的內外毛刺必須刮除。毛刺產生的原因是:(1)剪切刀刃變鈍,間隙過大;鋸片遲鈍,或安裝不當;(2)沖頭磨損或安裝不當;(3)火焰切割操作不當;(4)焊接制度不規范。防止和消除毛刺的辦法有:(1)正確安裝剪切、鋸切和沖孔裝置;(2)及時更換磨損的刀刃、鋸片和沖具;(3)加強產品切割操作的管理;(4)調整焊接制度.

一般產品允許有一定高度的毛刺存在;焊管的內外毛刺必須刮除.

|

毛刺類型 |

描述 |

|

|

1 |

串珠狀毛刺 |

呈柱狀或水滴狀,金屬表面光亮,附著牢固 |

|

2 |

碎土狀毛刺 |

呈細碎土狀,毛刺附著,較容易去除 |

|

3 |

碎玻璃狀毛刺 |

呈碎玻璃狀,邊緣鋒利。部分高強度附著,切割表面的下側毛糙 |

|

4 |

細齒狀毛刺 |

呈細齒邊緣鋒利附著在切割面下側 |

毛刺 專用HD諧波減速機FHA-8C-50-E200A-C二、電路設計中常用詞。數字電路中常將毛刺定義為采樣間越過邏輯門限一次以上的任何跳變,主要是指電路輸出波形中含有時間很短有規律或沒有規律的脈沖而又對設計沒有用處或產生其他影響,一般都要考慮去除毛刺。通常可以通過加某些元件(如電容濾波)或者改變電路設計實現消除毛刺。

詳細:

信號在FPGA器件內部通過連線和邏輯單元時,都有一定的延時。延時的大小與連線的長短和邏輯單元的數目有關,同時還受器件的制造工藝、

圖6.21給出了一個邏輯冒險的例子,從圖6.22的仿真

毛刺 專用HD諧波減速機FHA-8C-50-E200A-C圖6.22 圖6.21所示電路的仿真波形

判斷一個邏輯電路在某些輸入信號發生變化時是否會產生冒險,首先要判斷信號是否會同時變化,然后判斷在信號同時變化的時候,是否會產生冒險,這可以通過邏輯函數的卡諾圖或邏輯函數表達式來進行判斷。對此問題感興趣的讀者可以參考有關脈沖與數字電路方面的書籍和文章。

如何處理毛刺

我們可以通過改變設計,破壞毛刺產生的條件,來減少毛刺的發生。例如,在數字電路設計中,常常采用格雷碼計數器取代普通的二進制計數器,這是因為格雷碼計數器的輸出每次只有一位跳變,消除了競爭冒險的發生條件,避免了毛刺的產生。

毛刺并不是對所有的輸入都有危害,例如D觸發器的D輸入端,只要毛刺不出現在時鐘的上升沿并且滿足數據的建立和保持時間,就不會對系統造成危害,我們可以說D觸發器的D輸入端對毛刺不。 根據這個特性,我們應當在系統中盡可能采用同步電路,這是因為同步電路信號的變化都發生在時鐘沿,只要毛刺不出現在時鐘的沿口并且不滿足數據的建立和保持時間,就不會對系統造成危害。 (由于毛刺很短,多為幾納秒,基本上都不可能滿足數據的建立和保持時間)

以上方法可以大大減少毛刺,但它并不能完全消除毛刺,有時,我們必須手工修改電路來去除毛刺。我們通常使用"采樣"的方法。 一般說來,冒險出現在信號發生電平轉換的時刻,也就是說在輸出信號的建立時間內會發生冒險,而在輸出信號的保持時間內是不會有毛刺信號出現的。如果在輸出信號的保持時間內對其進行"采樣",就可以消除毛刺信號的影響。

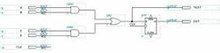

有兩種基本的采樣方法:一種方法是在輸出信號的保持時間內,用一定寬度的高電平脈沖與輸出信號做邏輯"與"運算,由此獲取輸出信號的電平值。圖6.23說明了這種方法,采樣脈沖信號從輸入引腳"SAMPLE"引入。從圖6.24的仿真波形上可以看出,毛刺信號出現在"TEST"引腳上,而"OUT"引腳

圖6.23 消除毛刺信號的方法之一

圖6.24 圖6.23所示電路的仿真波形

圖6.26 圖6.25所示電路的仿真波形 存在邏輯冒險的電路示例圖6.21 存在邏輯冒險的電路示例

存在邏輯冒險的電路示例圖6.21 存在邏輯冒險的電路示例

仿真波形冒險往往會影響到邏輯電路的穩定性。時鐘端口、清零和置位端口對毛刺信號十分,任何一點毛刺都可能會使系統出錯,因此判斷邏輯電路中是否存在冒險以及如何避免冒險是設計人員必須要考慮的問題。

仿真波形冒險往往會影響到邏輯電路的穩定性。時鐘端口、清零和置位端口對毛刺信號十分,任何一點毛刺都可能會使系統出錯,因此判斷邏輯電路中是否存在冒險以及如何避免冒險是設計人員必須要考慮的問題。

毛刺上的毛刺已被消除了.

毛刺上的毛刺已被消除了.

毛刺上述方法的一個缺點是必須人為的保證sample信號必須在合適的時間中產生,另一種更常見的方法是利用D觸發器的D輸入端對毛刺信號不的特點,在輸出信號的保持時間內,用觸發器讀取組合邏輯的輸出信號,這種方法類似于將異步電路轉化為同步電路。 圖6.25給出了這種方法的示范電路,圖6.26是仿真波形。

毛刺上述方法的一個缺點是必須人為的保證sample信號必須在合適的時間中產生,另一種更常見的方法是利用D觸發器的D輸入端對毛刺信號不的特點,在輸出信號的保持時間內,用觸發器讀取組合邏輯的輸出信號,這種方法類似于將異步電路轉化為同步電路。 圖6.25給出了這種方法的示范電路,圖6.26是仿真波形。

毛刺圖6.25 消除毛刺信號方法之二

毛刺圖6.25 消除毛刺信號方法之二

毛刺在仿真時,我們也可能會發現在FPGA器件對外輸出引腳上有輸出毛刺,但由于毛刺很短,加上PCB本身的寄生參數,大多數情況下,毛刺通過PCB走線,基本可以自然被慮除,不用再外加阻容濾波。

毛刺在仿真時,我們也可能會發現在FPGA器件對外輸出引腳上有輸出毛刺,但由于毛刺很短,加上PCB本身的寄生參數,大多數情況下,毛刺通過PCB走線,基本可以自然被慮除,不用再外加阻容濾波。